流水线

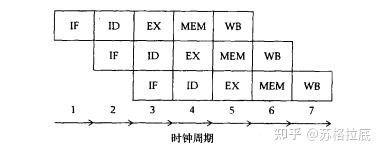

在计算机体系结构中,并行性的最早应用之一是使用流水线将一个复杂的操作分成一系列独立的段,如果不同的段使用不同的资源,且它的前一个操作完成了第一段,立即启动一个操作,这样就能重复执行其他的操作。

流水包括下面的这些级:

取指令(IF)

指令译码(ID)

执行(EX)

存储访间(MEM)

回写(WB)

取指和译码是自明的。为执行的目的,将EX和MEM级组织在一起。

如果指令是一条寄存器到寄存器操作,它能在算术逻辑部件(ALU)中实施,则这一条指令在EX级完成。

如果它是一条存储访问指令,则地址计算在EX级实现,而存储访问实际上是在MEM级发生。

注意,如果需要的存储单元不在高速缓存中,出现不命中,那么这条指令将停顿(stall)直到将需要的块(block)装人高速缓存中。如果指令是分支指令,那么在执行阶段用一个指定寄存器与0比较并在MEM级将PC置成正确的值。WB级用来将数据写回到寄存器中;在分支指令中不使用它。

例子

ADD R1, R2, R3

SUB R4, R1, R5

这样的指令序列能没有延地被执行,因为加法指令的结果是直接被送到减法指令的执行级,而不用等待回写到寄存器中。然而,这在

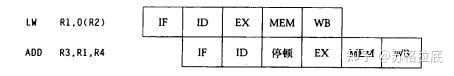

LW R1, 0(R2)

ADD R3, R1, R4

序列是不可能的,因为在存储周期结束前,取数指令的结果是不可能得到的。因此,我们看到如下图所描绘的一个周期的停顿。

在上面load和add指令之间插人一条这样的指令,它不使用那个正在取数的寄存器,编译器调度就能消除此问题。

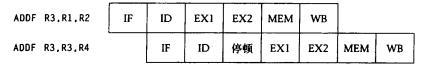

A+B+C

其中浮点加的流水线需要两级。如果按从左到右的顺序对表达式求值,那么第二条加法指令在执行前将不得不等待一个周期,如下图所示。